# All-Optical Clock Recovery From Short Asynchronous Data Packets at 10 Gb/s

N. Pleros, K. Vrysokinos, C. Bintjas, K. Yiannopoulos, K. Vlachos, H. Avramopoulos, and G. Guekos

**Abstract**—In this letter, we demonstrate clock extraction from 10-Gb/s asynchronous short data packets. Successful clock acquisition is achieved from data packets arriving at time intervals of only 1.5 ns, irrespective of their precise phase relation. The clock recovery circuit used consists of a Fabry–Pérot filter and an ultrafast nonlinear interferometer gate and requires very short time for synchronization.

**Index Terms**—Burst mode, clock recovery, optical packet/burst switching, semiconductor optical amplifier (SOA), ultrafast nonlinear interferometer (UNI).

## I. INTRODUCTION

OPTICAL PACKET switching has been introduced as the main concept to overcome limitations related to optical–electrical–optical conversions and to fully exploit bandwidth capacity, especially as it offers distinguishing advantages such as on-demand use of bandwidth and the ability to switch bursty traffic [1]. However, the lack of a simple and reliable optical memory that can store and retrieve the information bit by bit as well as the bursty nature of the traffic profile, imposes the need for dynamically switched optical nodes that are able to handle asynchronous packets from different sources on their way to different destinations [2], [3]. In order to efficiently manage such short asynchronous optical packets, it is crucial to be able to extract asynchronously the clock signal on a packet-by-packet basis.

Several techniques have been proposed for all-optical clock recovery, including synchronized mode-locked ring lasers [4], electronic phase-locked loops [5], and self-pulsating distributed feedback (DFB) lasers [6], [7]. Ring lasers and phase-locked loops require a long time for synchronization to the data streams and are not suitable for asynchronous short optical packet traffic. Self-pulsating DFBs require significantly less overhead for clock acquisition and have been demonstrated to operate successfully with asynchronous data packets comprised of a few thousands of bits and guard bands of a few hundreds of bits [6], at rates up to 40 Gb/s [7]. Recently, we have demonstrated a novel clock recovery circuit that acquires clock, within a few (2) bits, from short (30-b long) packets [8]

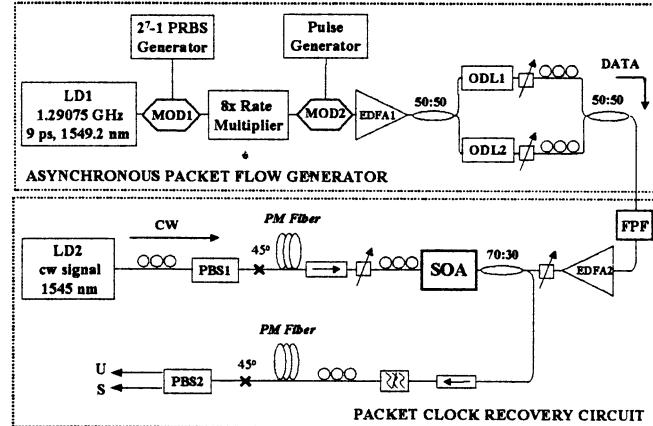

Fig. 1. Experimental setup.

and which, for this reason, can in principle reduce the guard band overhead between packets. This circuit was also used in a proof-of-principle experiment to demonstrate all-optical header from payload separation [9]. The circuit uses a low-finesse Fabry–Pérot filter (FPF) followed by a semiconductor optical amplifier (SOA)–based ultrafast nonlinear interferometer (UNI) [10], [11]. The FPF is used to partially fill the “0s” in the incoming data stream from the preceding “1s” and to create a signal that resembles the packet clock but is amplitude modulated, while the UNI is used to remove this amplitude modulation.

In the present communication, we show that the FPF/UNI gate clock recovery circuit can acquire clock from asynchronous data packets at 10 Gb/s, as would be encountered in the receiver of a “real-life” node. To underline the capability of the circuit, we use short (41 b long) test packets and show, for the first time to our knowledge, clock acquisition from asynchronous packets, arriving at time intervals of as short as 1.5 ns between them. The proposed circuit is self-synchronizing, requires no high-speed electronics, and can find applications in burst mode, packet receivers, or all-optical signal processing circuits.

## II. EXPERIMENT

Fig. 1 shows the experimental configuration that consists of two main subsystems; the asynchronous packet flow generator and the packet clock recovery circuit. A gain-switched DFB laser (LD1) at 1.29075 GHz, provided 9-ps pulses at 1549.2 nm after linear compression. This pulse train was modulated with a  $2^7 - 1$  pseudorandom binary sequence signal from a pattern generator and a LiNbO<sub>3</sub> modulator (MOD1) and was three-times bit interleaved to generate a 10.326-Gb/s pseudodata stream.

Manuscript received December 23, 2002; revised May 19, 2003.

N. Pleros, K. Vrysokinos, C. Bintjas, K. Yiannopoulos, and H. Avramopoulos are with the Department of Electrical and Computer Engineering, National Technical University of Athens, GR 15773 Athens, Greece (e-mail: npleros@cc.ece.ntua.gr).

K. Vlachos is with Bell Laboratories, Lucent Technologies, 1200BD Hilversum, The Netherlands (e-mail: kvlachos@lucent.com).

G. Guekos is with the Swiss Federal Institute of Technology Zurich, ETH Zentrum, CH-8092 Zurich, Switzerland.

Digital Object Identifier 10.1109/LPT.2003.816117

Data packets of variable length and period were formed using a second modulator (MOD2) driven from a programmable pulse generator. The packet stream was amplified in erbium-doped fiber amplifier (EDFA1) and split into two different optical paths via a 3-dB fiber coupler. The two paths were made so as to provide a maximum of 17.9-ns relative delay between the split signals. Polarization controllers and attenuators were used to independently adjust the polarization state and power in the two branches. Variable optical delay lines ODL1 and ODL2 were also used to independently control the relative arrival time of the packets at the clock recovery circuit, so as to investigate the minimum acceptable delay between successive packets and to assess the circuit ability to operate with successive packets that are asynchronous at the bit level. The asynchronous packet stream was then launched into the packet clock recovery circuit, which consists of an FPF and a UNI gate, powered by a continuous-wave (CW) signal at 1545 nm (LD2). The FPF had a free-spectral range equal to the line rate and a finesse of 20.7, corresponding to a  $1/e$  lifetime roughly of 7 b. The output of the filter was amplified in EDFA2 and inserted into the UNI gate as the control signal. The UNI gate was optimized for operation at 10 Gb/s and used polarization maintaining fiber at the input and output ports of the SOA to induce 50 ps of differential delay between the two orthogonal polarization components of the CW signal. The active element was a 1.5-mm bulk InGaAsP-InP ridge waveguide SOA with 27-dB small signal gain at 1550 nm, 24 dB at 1545 nm, 3-dB polarization gain dependence and a recovery time of 100 ps, when driven with 700-mA dc current. After exiting the SOA, the polarization components of the CW signal were filtered in a 2-nm filter, had their relative delay removed, and were made to interfere in polarization beam splitter (PBS2). The interferometer was biased so that, in the absence of the control signal, the CW signal appeared at its unswitched port (U) while in the presence of the control it appeared at its switched port (S).

### III. RESULTS AND DISCUSSION

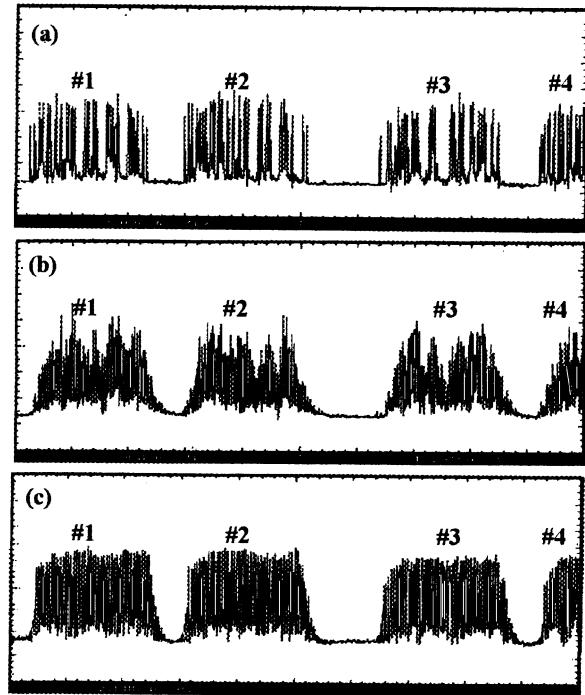

Data packets of different length, period, and content were used to evaluate the performance of this clock recovery scheme for asynchronous packet stream at 10 Gb/s. Fig. 2(a) shows a typical data stream, obtained from the asynchronous packet flow generator. More specifically, a sequence of four data packets is illustrated, each packet containing 41 b (approximately 4-ns duration). Packets #1 and #3 are traveling through the upper and Packets #2 and #4 are traveling through the lower branch of the packet generator. The coarse relative delay between Packets #1 and #2 was 1.5 ns and between Packets #2 and #3 2.9 ns. Packets #2 and #3 are shown in more detail in Fig. 3(a) and (b), respectively.

At the FPF, the asynchronous packet stream is convolved with the exponentially decaying response function of the filter, so that an amplitude modulated, but clock resembling signal is obtained. Fig. 2(b) shows the corresponding output of the FPF for Packets #1–#4. This is used as the control signal into the UNI gate to induce an almost  $\pi$ -phase shift between the orthogonal polarization components of the CW signal. This re-

Fig. 2. (a) Incoming asynchronous data stream of four packets and (b) corresponding FPF output, and (c) recovered packet clocks. The time base is 2 ns/div.

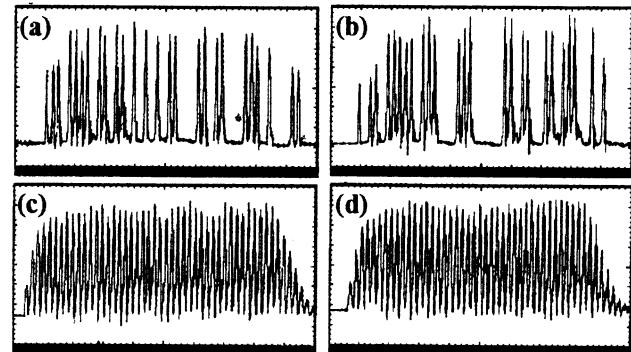

Fig. 3. (a), (b) Detailed representation of two incoming data packets and (c), (d) corresponding recovered packet clocks. The time base is 500 ps/div.

sults in a packet clock signal of nearly equal amplitude “1s” and very short rise and fall times. Fig. 2(c) shows the acquired packet clock signal. More detailed representation of the recovered packet clocks for Packets #2 and #3 is illustrated in Fig. 3(c) and (d).

The packet clocks display rise and fall times of 2 and 8 b, respectively, and amplitude modulation of less than 1.5 dB (highest to lowest pulse ratio), within the span of the original 41-b data packet. The circuit required 1 mW of optical power from the CW signal and 110 fJ/pulse from the data signal, corresponding to 0.9-mW average power for the packets shown here. Packet clocks of the same quality were obtained irrespective of the precise relative phase adjustment between the packets as set by the delay lines ODL1 and ODL2.

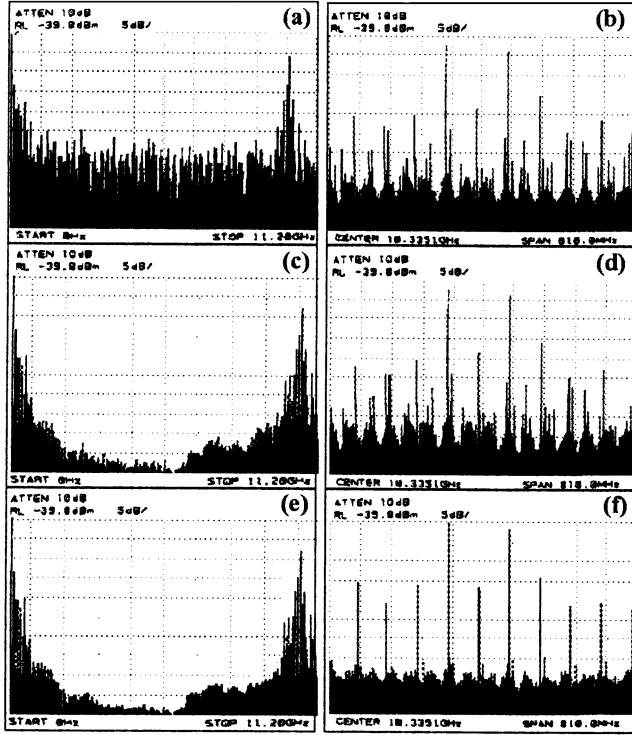

The quality of the asynchronously extracted clock signal was also examined using a 50-GHz microwave spectrum analyzer. Fig. 4(a) and (b) depict the RF spectrum of the packet

Fig. 4. RF spectrum of (a) incoming asynchronous data packets, (b), (c) corresponding FPF output, and (d) recovered packet clock. The span in (a), (b) is from dc to 11.2 GHz and in (c) and (d) the center frequency is around 10.326 GHz and the span is 810 MHz. The amplitude scale is 5 dB/div for all.

signal from dc to 11.2 GHz and within an 810-MHz band centered around the 10.326-GHz component, respectively. The asynchronous operation is confirmed by the suppressed clock component at 10.326 GHz with respect to the adjacent 80-MHz spaced packet subharmonics. Fig. 4(c) and (d) shows the corresponding output of the FPF. The effect of the filter is primarily to suppress all data modes outside a 500-MHz band around the base line rate. Data mode suppression within this 500-MHz band is achieved by taking advantage of the nonlinear transfer function of the deeply saturated SOA-based interferometric gate [8]. Fig. 4(e) and (f) shows the RF spectrum of the extracted packet clock at the output of the UNI gate for asynchronous traffic revealing data mode suppression in excess of 35 dB with respect to the 80-MHz spaced packet subharmonics. Finally, the root mean square timing jitter of the extracted clock was also calculated using the microwave spectrum analyzer for a total span of 3 kHz around the packet clock components and resolution bandwidth of 10 Hz, and was found to be less than 1 ps.

It should also be noted that the amplitude ratio between the 10.326-GHz clock component and the packet subharmonics has the same value in Fig. 4(b), (d), and (f), showing that the extracted clock retains the phase alignment of the initial asynchronous data stream. This amplitude ratio varies between a maximum value and zero, depending on whether the packets are perfectly phase aligned or misaligned by  $\pi$ , and this adjustment is provided by the setting of ODL1 or ODL2 within a bit-period time interval, approximately 100 ps.

#### IV. CONCLUSION

We have presented all-optical clock recovery from short, asynchronous 10-Gb/s data packets, arriving at time intervals of only 1.5 ns between them, by using a clock recovery circuit consisting of an FPF and a UNI gate. The scheme requires no high-speed electronics, is self-synchronizing and would be suitable for packet routing with all-optical techniques [12], [13], even in the asynchronous traffic regime. To achieve polarization independence, simplicity, and compactness, the circuit could be implemented using a fiber FPF and UNI gates constructed with low polarization-dependence SOAs or polarization-insensitive gates of the Mach-Zehnder type. Even though the circuit was demonstrated with 10-Gb/s packets, it is expected that its speed should be extendable to significantly higher rates since the CW signal plays the role of an optical holding beam [14] and helps to reduce the recovery time of the SOA.

#### ACKNOWLEDGMENT

The authors would like to thank R. Dall'Ara and S. Hansmann of Opto Speed, S.A. for providing the SOA and DFB lasers.

#### REFERENCES

- [1] C. Guillemot *et al.*, "Transparent optical packet switching: The European ACTS KEOPS project approach," *J. Lightwave Technol.*, vol. 16, pp. 2117–2134, Dec. 1998.

- [2] F. Masetti *et al.*, "Design and implementation of an optical burst/packet router prototype," presented at the Optical Fiber Communication Conf., Anaheim, CA, 2002, Paper FD1.

- [3] D. Wonglumsom *et al.*, "Experimental demonstration of an access point for HORNET – A packet-over-WDM multiple-access MAN," *J. Lightwave Technol.*, vol. 18, pp. 1709–1717, Dec. 2000.

- [4] K. Vlachos, G. Theophilopoulos, A. Hatzifremidis, and H. Avramopoulos, "30 Gb/s all-optical, clock recovery circuit," *IEEE Photon. Technol. Lett.*, vol. 12, pp. 705–707, June 2000.

- [5] D. T. K. Tong, K.-L. Deng, B. Mikkelsen, G. Raybon, K. F. Dreyer, and J. E. Johnson, "160 Gbit/s clock recovery using electroabsorption modulator-based phase-locked loop," *Electron. Lett.*, vol. 36, pp. 1951–1952, 2000.

- [6] D. Chiaroni *et al.*, "All-optical clock recovery from 10 Gbit/s asynchronous data packets," in *Eur. Conf. Optical Communication*, vol. 4, 2000, pp. 69–70.

- [7] B. Sartorius, C. Bornholdt, S. Bauer, and M. Mohrle, "40 GHz optical clock recovery for application in asynchronous networks," in *Eur. Conf. Optical Communication*, 2001, Paper We.P.32, pp. 442–443.

- [8] C. Bintjas *et al.*, "Clock recovery circuit for optical packets," *IEEE Photon. Technol. Lett.*, vol. 14, pp. 1363–1365, Sept. 2002.

- [9] ———, "All-optical packet address and payload separation," *IEEE Photon. Technol. Lett.*, vol. 14, pp. 1728–1730, Dec. 2002.

- [10] K. L. Hall and K. A. Rauschenbach, "100 Gbit/s bitwise logic," *Opt. Lett.*, vol. 23, pp. 1271–1273, Aug. 1998.

- [11] M. Tsurusawa, K. Nishimura, and M. Usami, "First demonstration of simultaneous demultiplexing from 80 Gb/s to  $2 \times 40$  Gb/s by SOA-based all-optical polarization switch," in *Eur. Conf. Optical Communication*, vol. 4, Amsterdam, The Netherlands, 2001, Paper Th.F.1.1, pp. 500–501.

- [12] S. A. Hamilton and B. S. Robinson, "40-Gb/s all-optical packet synchronization and address comparison for OTDM networks," *IEEE Photon. Technol. Lett.*, vol. 14, pp. 209–211, Feb. 2002.

- [13] A. Carena, M. D. Vaughn, R. Gaudino, M. Shell, and D. J. Blumenthal, "OPERA: An optical packet experimental routing architecture with label swapping capability," *J. Lightwave Technol.*, vol. 16, pp. 2135–2145, Dec. 1998.

- [14] R. J. Manning, D. A. O. Davies, S. Cotter, and J. K. Lucek, "Enhanced recovery rates in semiconductor laser amplifiers using optical pumping," *Electron. Lett.*, vol. 30, pp. 787–788, May 1994.